Demand For Timing Innovation Grows

The semiconductor industry has begun exploring a range of timing options as demand for increased performance and more features exceeds the ability to design chips using the same techniques and technology that have been relied on for decades.

Like many elements in computing, timing is a hierarchy or stack. It includes everything from partitioning AI computations into multiple parts and assembling the results concurrently, to making sure the different components in an advanced package or on an PCB or end device are working in their proper sequence. No device works well without proper timing, and some don’t work at all. Timing affects every facet of computing, from the amount of energy and time it takes to process data, to the accuracy of those results. In complex chips, timing even needs to take into account dependencies between different components under different use models and stresses.

Timing is not a new problem, but it is certainly getting far more complicated. Quartz crystal oscillators date back to the 1920s, when they were used to stabilize radio signals. They have been used in digital circuits for decades, as well. But much has changed in recent years. What used to be discrete components on a PCB increasingly are bundled together into a heterogeneous SoC or advanced package, often containing multiple power rails, and targeted at specific domains, from mobile devices to the cloud.

“The key infrastructure market segments are 5G radio access networks, data centers, and optical networks,” said James Wilson, vice president and general manager for timing products at Skyworks Solutions. He noted that demand is growing, particularly from the infrastructure markets, for higher performance, lower jitter, and more integrated timing solutions.

This becomes more difficult as data speeds increase, however. Optical and data center markets are ramping deployments at 400Gbps, with 800Gbps on the near horizon, and terabit speeds in development. “As networks are upgraded to higher bandwidths, hardware designs transition to using higher-speed PHY/SerDes technology,” Wilson said. “For example, over the last several years, optical and data center transitioned from 28Gbps PHYs to 56Gbps and 112Gbps PHYs.”

Along with those higher speeds come higher-density chips, which require tighter tolerances for everything. “Higher-speed networks are driving the need for more high-performance timing solutions,” he said. “State-of-the-art applications now require maximum reference clock jitter of less than 70 femtoseconds.”

At advanced process nodes, in particular, there is much less wiggle room when it comes to timing fluctuations. So any process variation, which may have gone unnoticed at 28nm, can present a major issue at 5nm, where there is far less margin available buffer that variation.

“Variation goes up, and variation grows exponentially with lower voltage,” said Mo Faisal, president and CEO of Movellus. “So on-chip variation becomes timing margin, which becomes fmax, which goes back to Vmin. It’s a vicious cycle, and you keep going back and forth until you figure it out. Some margin depends on the technology, some depends on the functionality and different modes. If you have different P states in a multicore processor, for example, where half the cores are on and you want to go to 100% utilization temporarily, then you’re turning on those processor cores and putting a lot of pressure on the supply network. That causes droop, and unless you do some smart things with the droop, that ends up eating into your margin, which eats into your Vmin. “

A fast-changing market

Continued device shrinks and lower power requirements are a huge challenge in the timing world. “You want the same kind of jitter, but much lower power and smaller size in certain applications, which is becoming tougher and tougher by the day,” said Yimu Guo, Renesas timing product manager.

As of today, the timing market is highly fragmented. Each deployment requires a different balance of priorities. “Finding the right mix, the sweet spot for your product complexity and performance — and meeting the size and the cost target at the same time — is the challenge with the timing market right now,” Guo said. “You have to segment it the right way to make sure that the market is served.”

This explains why Renesas offers three different brands of timing solutions aimed at meeting different performance and complexity targets. “Even within one application space, if you talk to one customer, that customer’s requirements might be very different from another’s because it depends on the engineer’s level of confidence and the way that they’re typically going to lay the board,” Guo said.

What’s striking in looking at those three brands is how quickly the paradigm keeps shifting. The latest release of Renesas’ flexible, low-power offering features a performance level that until recently was available only in its high-performance solution. “High-performance today is low-performance two years from now,” he said.

Performance needs to be considered over time, as well, because timing can shift in the same device as it ages, or within particular segments of a heterogeneous design based upon a variety of factors, including use cases and end applications. The problem is that no one solution or approach works with all designs.

“It’s not just a methodology,” said Movellus’ Faisal. “There has to be some IP that detects what’s happening in silicon, and then compensates for it. It’s done more through smarts, as opposed to just having a methodology that applies everywhere. By definition, you’re over-designing. But if you have a way of bridging the gap between what’s happening to silicon, like whether there’s variation in this chip, then you can automatically compensate for that at runtime. So a platform for all kinds of chips with a singular methodology is the most efficient thing to do. But it’s actually inefficient from a PPM perspective if you want all the chips to be customized.”

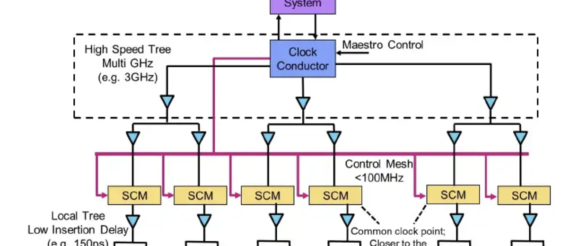

Fig. 1: Movellus’ intelligent clock scheme. Source: Movellus

The price of progress

Ongoing developments in the timing market reflect significant changes in the electronics world over the last several years. “A car in 1978 had one electronic control unit and eight semiconductor devices in it,” said Piyush Sevalia, executive vice president of marketing at SiTime. “A car from 2022 has 80 ECUs and 8,000 semiconductor devices in it. You’re seeing more and more semiconductor usage in cars, a lot more processors, more data transfer units — and all of those things are going to need timing.”

A car can be a uniquely challenging environment. “It’s got to be able to start up in -40° C, it’s got to be able to operate when the engine is running at 125° C, and it’s got to be able to operate on bumpy roads and smooth roads. So there are inherent shock components that come into play – it’s constantly vibrating as it’s moving,” Sevalia said.

The same is true in 5G RRU (remote radio unit) deployments. “These devices are subject to the forces of nature,” Sevalia said. “What we are seeing is that electronics as a whole is being deployed in environments which are not pristine anymore.”

This is true whether you’re mounting a device on the sides of stadiums that vibrate as people move through them, or mounting them outdoors in the middle of Florida where they have to operate through a hurricane. And those challenges likely will continue to move to the forefront, along with growing concerns about size.

“Ten years ago, when we were talking to our customers, there was no mention of size in infrastructure, radios, base stations, things like that,” he said. “Today, they are concerned about size – and it’s not just the X-Y footprint, it’s also the Z footprint, because as they populate these line cards inside the equipment, there has to be room to pump air through it so you can take the heat out.”

Lower power, Sevalia said, is also an increasing priority, and not just in the more obvious areas like mobile IoT. “Even on the infrastructure side, people are looking at power consumption and saying we need to cut the power consumption down,” he said. “And that’s a challenge in itself because as you’re trying to pump more data, and as your clock signal needs to get clear, one way to get it cleaner is to burn more power – but you can’t.”

Finding a solution

Because timing is a hierarchy, solutions need to be developed up and down the stack, following data from point of creation to wherever it is processed and stored.

Sevalia said the challenges of meeting the demand for an end device that’s more immune to vibration, shock, and temperature changes, along with the ever-growing demand for higher performance, lower power, and smaller size, have led SiTime to use MEMS instead of quartz for timing. “People have used quartz for the longest time, so they take quartz reference for granted,” he said. “And now we’re coming in and saying, ‘Look, there’s a different way to do it.’”

Looking beyond quartz can offer key benefits regarding temperature and vibration. As an example, consider a big board that might be subject to more board-bending stress at the center than at the edges. “In the quartz case, you might have to mount the devices on the edge of the board so they’re not subject to that stress,” he said. “In our case, you can put it wherever you want.”

Skyworks’ Wilson noted that design engineers also are looking for ways to address many of these issues through functional integration. “System designers are seeking solutions that unify all clock generation and clock distribution in a single IC,” he said. “This helps the design meet stringent performance requirements while simplifying PCB footprint and power budgeting.”

Integrated acoustic resonators

In a recent paper, researchers at Purdue University, Texas Instruments, and Skyworks detailed a method of integrating acoustic resonators into chips using the components that are already there.

One of the paper’s authors, Dana Weinstein, a professor of electrical and computer engineering at Purdue University, said the key aim was to eliminate the need for an off-chip crystal frequency reference entirely. A quartz reference, she said, “is bulky and requires a wire pin to get the electric signal onto your chip. It’s too low-frequency, so you have to multiply up the frequency. And it’s noisy, and it’s power-consuming to distribute that signal everywhere on your chip.”

Still, she acknowledged that any effort to do so faces significant challenges. “It’s a rather complicated geometry, and it means we have to work with a lot of constraints of whatever that CMOS foundry has defined and optimized for digital circuits,” Weinstein said. “We can’t mess around with all of the different layers. We can’t choose our materials. So you have to come up with innovative ways to confine the vibrations. There’s a lot of optimization involved in design, in figuring out what vibrations can exist in a stack and then taking advantage of those.”

Replacing traditional quartz crystals with other materials, Weinstein said, doesn’t eliminate the essential issue the Purdue team is trying to solve. “Aluminum nitride and other piezoelectric materials are already replacing quartz for that tuning element in the radio, but it’s a separate type of microfabrication and microelectronics process that requires different capabilities, different materials, and different packaging than what the CMOS foundries require,” she said.

Supply chain and security

Those different materials and different packaging, Weinstein said, then require different manufacturing infrastructure for each specialized chip. “So that brings additional vulnerabilities in terms of supply chain, as well as in terms of our capabilities here in the U.S. and the time it takes to ramp those up,” she said. “A lot of that manufacturing happens externally to the U.S., especially the packaging side right now.”

The research promises to sidestep those kinds of supply chain challenges. “What we’re doing eliminates that extra chip, eliminates the other materials, and even eliminates the packaging,” Weinstein said. “Because the vibrating structure is embedded within the CMOS at the transistor level, you can avoid that altogether.”

It also has the potential to reduce security vulnerabilities when compared with established practices, whether those leverage a quartz crystal reference or something else. “Either way, you have to cross chips, and so there’s a pin that gives direct access to the clock,” Weinstein said. “And if you glitch that clock, if someone manages to get access to that electrical pin, then the entire microprocessor chip is compromised. If you can embed those references instead, and there’s no external pin to the clock, then that makes it more secure from that perspective.”

A single integrated solution, Weinstein said, is also easier to check for possible tampering. “If I can excite vibrations inside my chip once it’s packaged, once it’s out in the field, I can do things like ultrasonic imaging of the chip in situ and interrogate, ‘Has it been tampered with? Is the package okay?’ And I can do that at any point,” she said.

That ability to detect tampering is particularly useful if you have to send the chip to a non-trusted site. “That happens a lot now, because we don’t have those full capabilities in trusted foundries in the U.S,” Weinstein said. “So if I have to send it off for this part of the process, then over to another country for that part of the process, someone could tamper with the design, or insert a hardware Trojan, or mess with some wiring that’s impossible to detect when you get your chip back – unless you can interrogate it from within.”

Conclusion

Crucially, Weinstein noted that the research was done using standard chips. “We fabricated this in standard CMOS,” she said. “We just taped out in standard 14nm technology that’s available to the general public through multi-project wafers. There was nothing special that was done to the chip afterwards. It’s just direct from foundry.”

Still, significant limitations remain before this kind of solution can reach the market. “While we’ve demonstrated the capability for resonance on these chips, the signal is pretty small that’s coming out of these, and so there are additional challenges to closing the feedback loops to make a resonator into an oscillator – into a clock,” Weinstein said. “So we are working on oscillator designs that can do that in standard CMOS.”

But she noted that’s going to take time. “That’s something to look forward to as ferroelectric materials emerge in more advanced technology nodes, and they’re primed to do so in the next few years,” she said. “Foundries have already developed them. It’s a matter of getting into product at this point. And once that door is open, the performance of oscillators, of actual clocks on chip, is just one step away – with zero barrier to entry into standard technology.”

— Ed Sperling contributed to this report.